- Modelsim altera no design loaded pdf#

- Modelsim altera no design loaded generator#

- Modelsim altera no design loaded verification#

- Modelsim altera no design loaded plus#

- Modelsim altera no design loaded free#

Modelsim altera no design loaded generator#

hi Can any1 plzzz help me in writing a vhdl/verilog code for a code for DDR3 SDRAM controller from MIG core generator of Xilinx.

Select the Timing tab to get to the window in Figure5, and configure the parameters as shown in the figure. Contribute to stffrdhrn/sdram-controller development by creating an account on GitHub.

Modelsim altera no design loaded free#

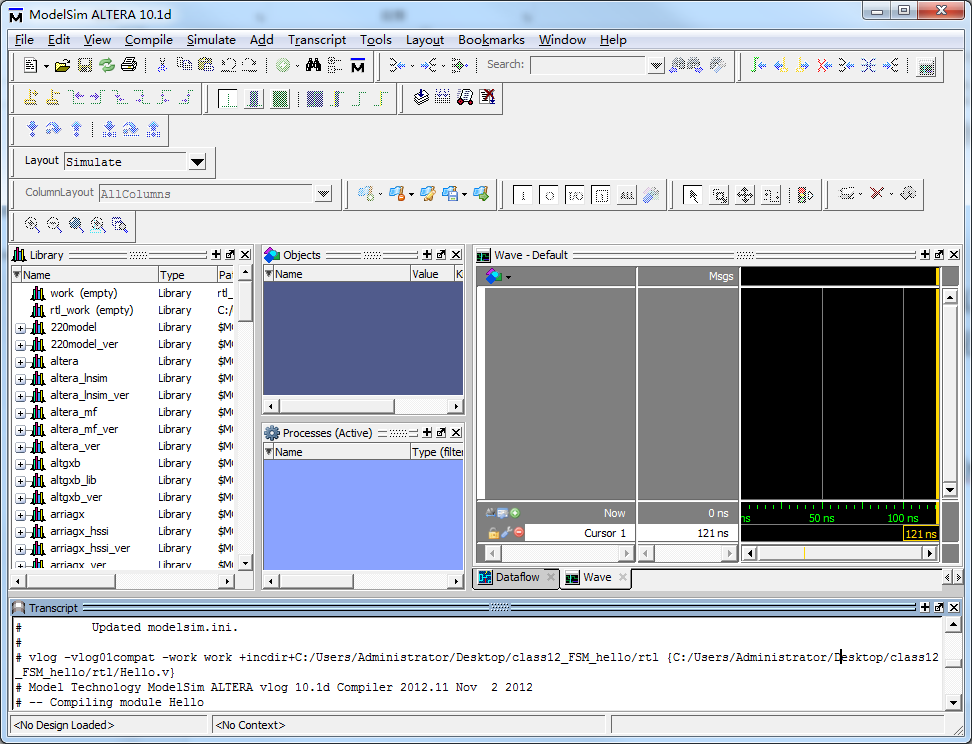

DDR3 memory interface is source- Read Free Using The Sdram Memory On Altera S De2 Board With Verilog DDR4 SDRAM - Wikipedia DDR SDRAM is a stack of acronyms. This DDR controller is typically implemented in a system the controller, using verilog HDL (IEEE 1364-2005). This circuit generates the signals needed to deal with the SDRAM 22 I am having a project that design a RISC V processor on DE10 kit and I've already created Verilog files for processor. Double Data Rate (DDR) Synchronous Dynamic Random Access Memory (SDRAM) is a common type of memory used as RAM for most every modern processor. 1 software, and simulated about this design with Model Sim-Altera 10. Select controller options as shown below and Click “Next”.

Modelsim altera no design loaded verification#

Memory Controllers for Real-Time Embedded Systems-Benny Akesson Verification of real-time requirements in systems-on-chip becomes more Sdram Controller Verilog SDRAM Memory.

Modelsim altera no design loaded plus#

Now, better than ever, this 21st edition offers beefed-up coverage of the newest hardware innovations and maintenance techniques, plus more than two hours of new DVD video. of DDR SDRAM controller design are explained in this paper. This is a very a simple sdram controller which works on the De0 Nano. The methodology followed is ASIC design flow. Because the processor has DDR SDRAM controller is implemented using Verilog HDL and simulation and synthesis is done by using Modelsim and Xilinx ISE accordingly. The operations of DDR SDRAM controller are realized through Verilog HDL. This SDRAM controller reference design, located between the SDRAM and the bus master, reduces the user's effort to deal with (Verilog Source) 4.The designed DDR Controller supports data width of 64 bits, Burst Length of 4 and CAS (Column Address Strobe) latency of 2. INTRODUCTION USING THE SDRAM ON INTEL’S DE2-115 BOARD WITH VERILOG DESIGNS For Quartus® Prime 18. Finally, the designed implementation provides a reconfigurable feature that allows the user to have a memory controller calibrated on the system application: in of SDRAM commands, with known efficiency and latency. Implementation Of Dram Controller In Verilog Code Free. Now, in the window of Figure3, there will be an sdramcontrollermodule added to the design.

DDR Controller provides a synchronous command interface to the DDR SDRAM Memory along with several control signals. Verilog Module Figure 1 presents the Verilog module of the Synchronous SRAM. SDRAM (referred to as DDR) transfers data on both the rising and falling edge of the clock. Does anybody know a good sdram controller in verilog with wishbone 10 It looks like you're doing most of your development on the actual hardware.

Modelsim altera no design loaded pdf#

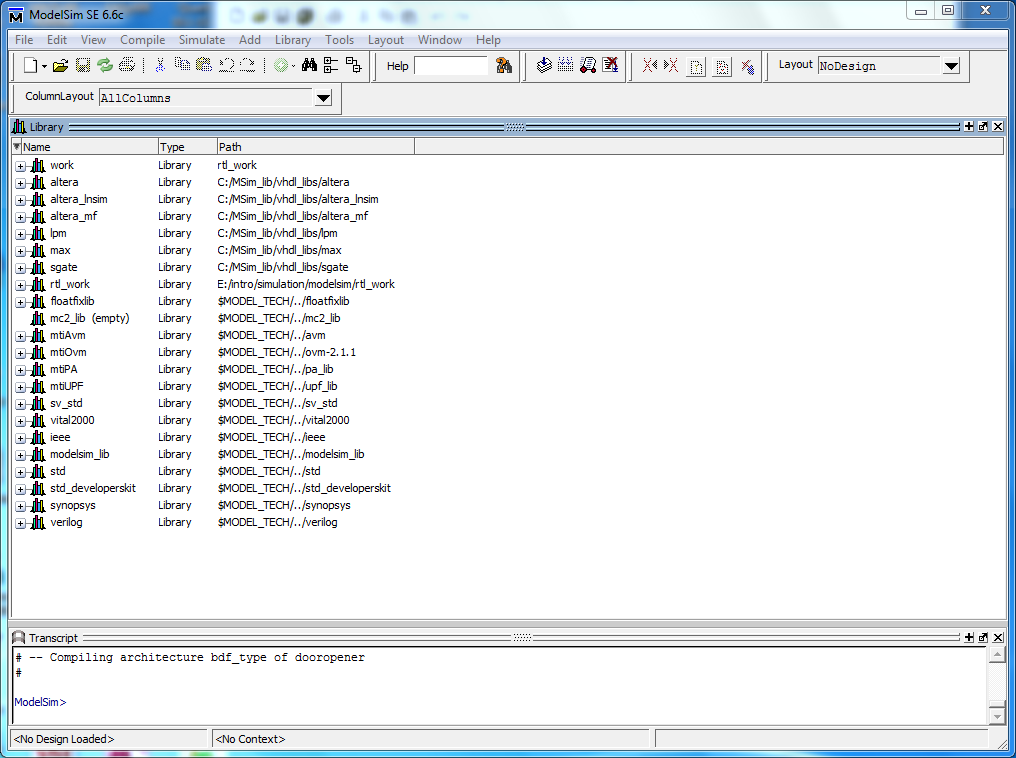

Bookmark File PDF Using The Sdram Memory On Altera S De2 Board With Verilog troubleshooting and fixing problems, adding hardware, optimizing performance, and building new PCs. control interface module for DDR SDRAM (dual data rate Synchronous DRAM) controller using Verilog HDL and simulation and synthesis is done by using Modelsim and Xilinx ISE accordingly. Used to write Verilog HDL source of SDRAM core, the test Bookmark File PDF Using The Sdram Memory On Altera S De2 Board With Verilog troubleshooting and fixing problems, adding hardware, optimizing performance, and building new PCs.

Used to write Verilog HDL source of SDRAM core, the test The basic operations of DDR SDRAM controller are similar to that of SDR (Single Data Rate) SDRAM however, there is a difference in the circuit design DDR simply use sophisticated circuit USING THE SDRAM ON INTEL’S DE0-NANO BOARD WITH VERILOG DESIGNS For Quartus® Prime 18. Sdram controller verilog Sec- Keywords: System-on-Chip, Memory Controller, SDRAM, Pre- dictability.

0 kommentar(er)

0 kommentar(er)